## 双向移位寄存器实验

# 双向移位寄存器实验

## 实验目的

1. 掌握双向移位寄存器电路结构和工作原理。

2. 掌握Quartus II软件环境和FPGA实验台的使用方法。

3. 掌握利用框图输入法设计双向移位寄存器电路的方法。

4. 验证双向移位寄存器功能。

## 实验内容

实现移位运算功能。完成双向移位寄存器电路的设计、仿真、编程下载和实验台演示。

# 双向移位寄存器

移位寄存器不仅能寄存数据，而且能在时钟信号的作用下使其中的数据依次左移或右移。移位寄存器可以用来寄存代码，还可以用来实现数据的串行-并行转换、数值的运算以及数据的处理等。

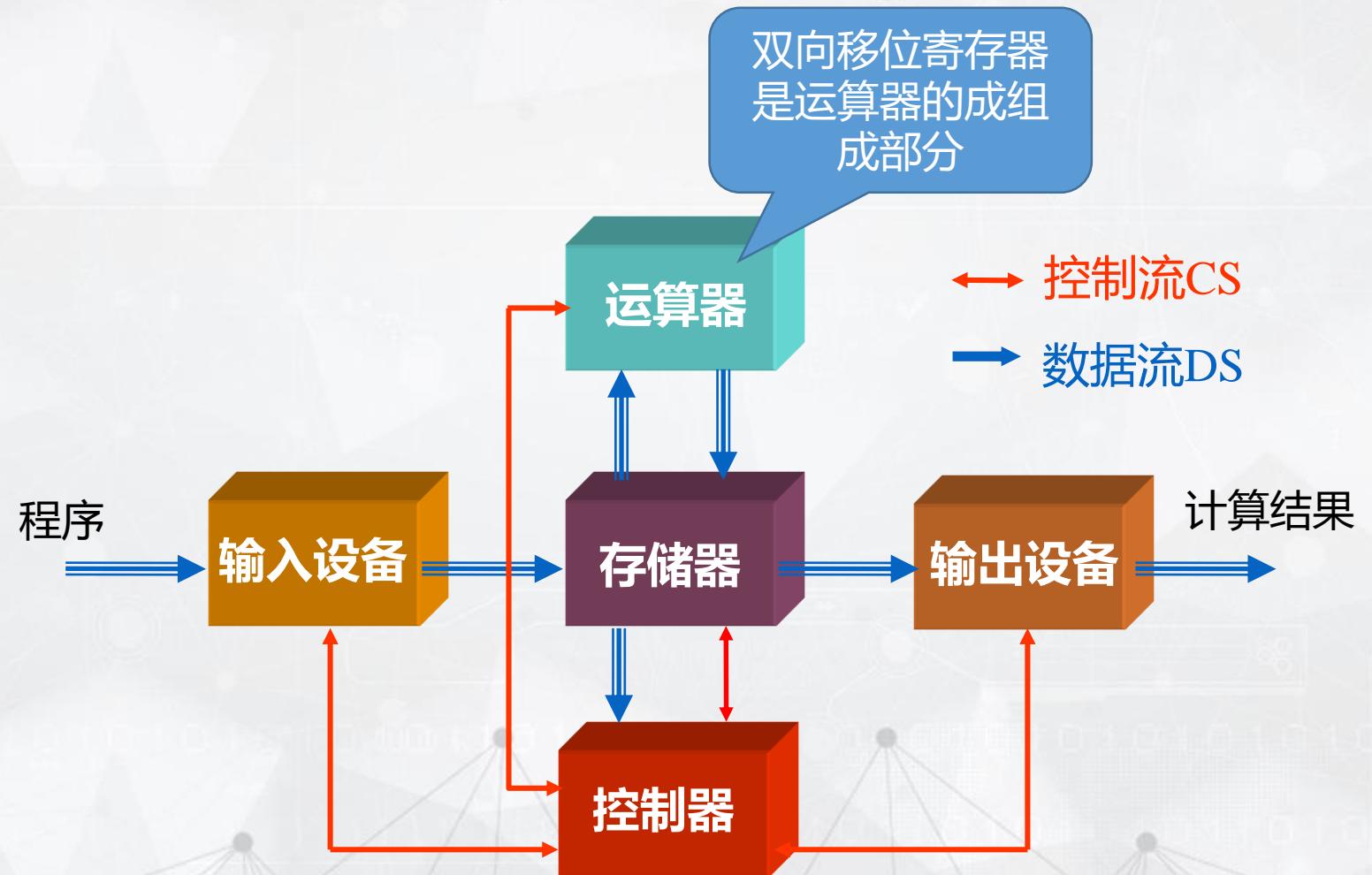

# 双向移位寄存器在基本模型机中的位置

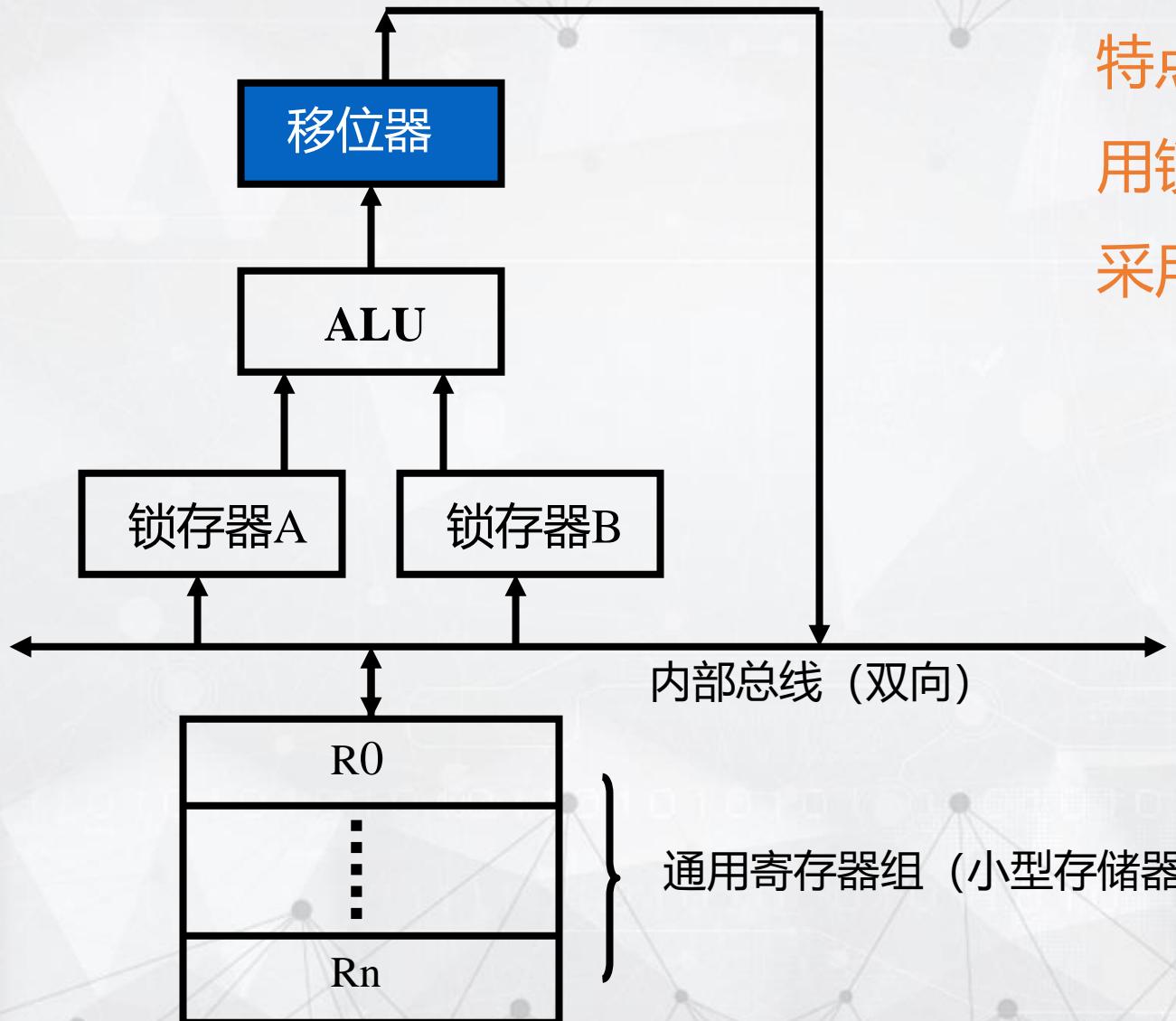

# 移位寄存器是运算器的重要组成部分

特点：

用锁存器暂存操作数；

采用双向内总线。

# 双向移位寄存器功能表

| 输入 |    |    |    | 输出             |                |                |                |                |                |                |                |                |         | 功能 |

|----|----|----|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---------|----|

| CP | S1 | S0 | M  | Q <sub>7</sub> | Q <sub>6</sub> | Q <sub>5</sub> | Q <sub>4</sub> | Q <sub>3</sub> | Q <sub>2</sub> | Q <sub>1</sub> | Q <sub>0</sub> | C <sub>N</sub> |         |    |

| ↑  | 0  | 0  | 任意 | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0       | 保持 |

| ↑  | 1  | 0  | 0  | D <sub>0</sub> | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | 循环右移    |    |

| ↑  | 1  | 0  | 1  | C0             | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | 带进位循环右移 |    |

| ↑  | 0  | 1  | 0  | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | D <sub>7</sub> | D <sub>7</sub> | 循环左移    |    |

| ↑  | 0  | 1  | 1  | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | C0             | D <sub>7</sub> | 带进位循环左移 |    |

| ↑  | 1  | 1  | 任意 | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | 0              | 装数      |    |

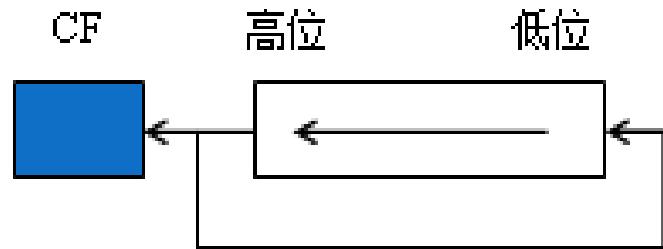

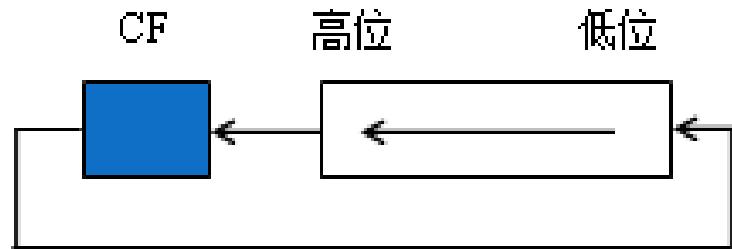

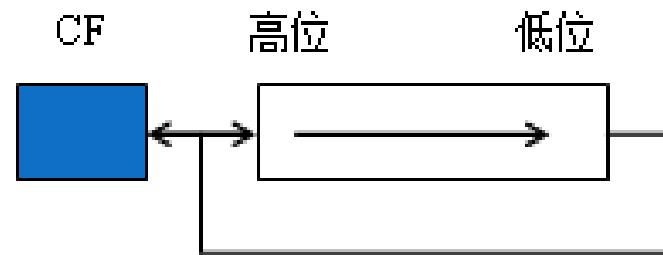

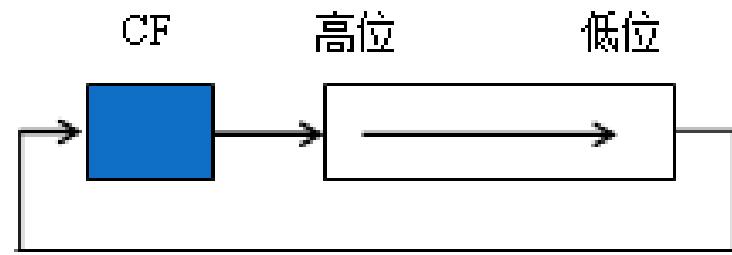

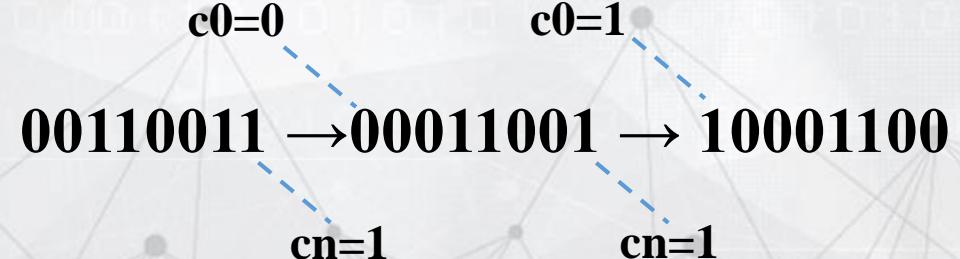

# 移位运算功能

(a) 循环左移

(b) 带进位循环左移

(c) 循环右移

(d) 带进位循环右移

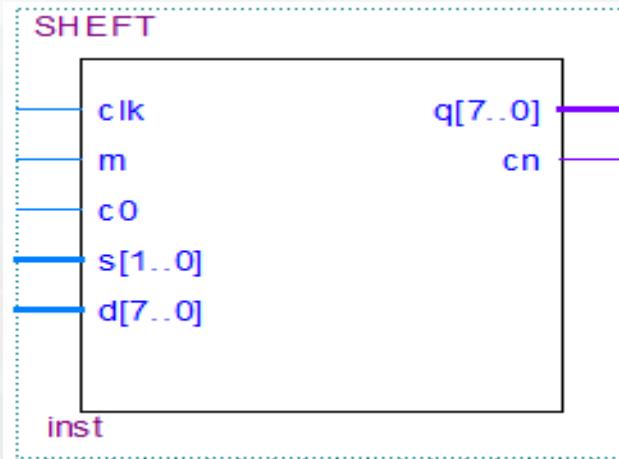

# 利用vhdl语言设计双向移位寄存器（部分参考代码）

```

library ieee;

use ieee.std_logic_1164.all;

entity sheft is

port(

clk, m, c0 : in std_logic;

s: in std_logic_vector(1 downto 0);

d: in std_logic_vector(7 downto 0);

q: out std_logic_vector(7 downto 0);

cn: out std_logic );

end entity;

```

```

architecture behav of sheft is

signal abc: std_logic_vector(2 downto 0);

begin

abc <= s & m;

process(clk,s)

variable reg8: std_logic_vector(8 downto 0);

variable cy: std_logic;

begin

if clk'event and clk = '1' then

if abc = "000" or abc = "001" then

reg8 := reg8;

end if;

if abc = "100" then

cy := reg8(0);

reg8(8) := cy;

reg8(7 downto 0):= reg8(8 downto 1);

end if;

....

```

# 实验任务与步骤

1、新建工程，新建vhdl文件（\*.vhd），设计输入双向移位寄存器vhdl代码。保存文件。

主菜单“File”→“New Project Wizard”，新建工程Sheft（实体名）

主菜单“File”→“New”项，选择VHDL File，新建vhdl文件，保存为 Sheft.vhd。

2、设置器件

主菜单“Assignmemts”→“Device”项，选择Cyclone IV E系列 EP4CE55F23C8芯片

3、编译电路

主菜单“Processing”→“Start Compliation”项，启动编译

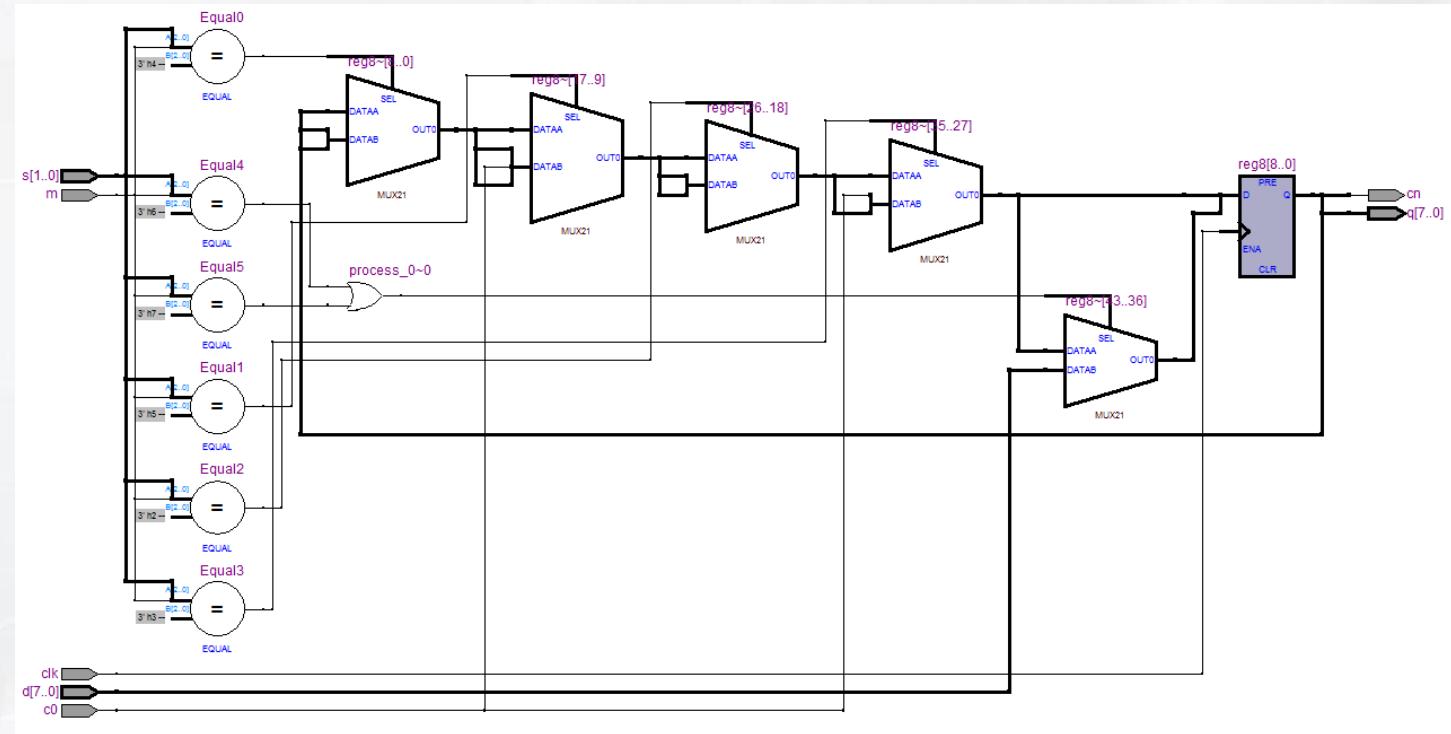

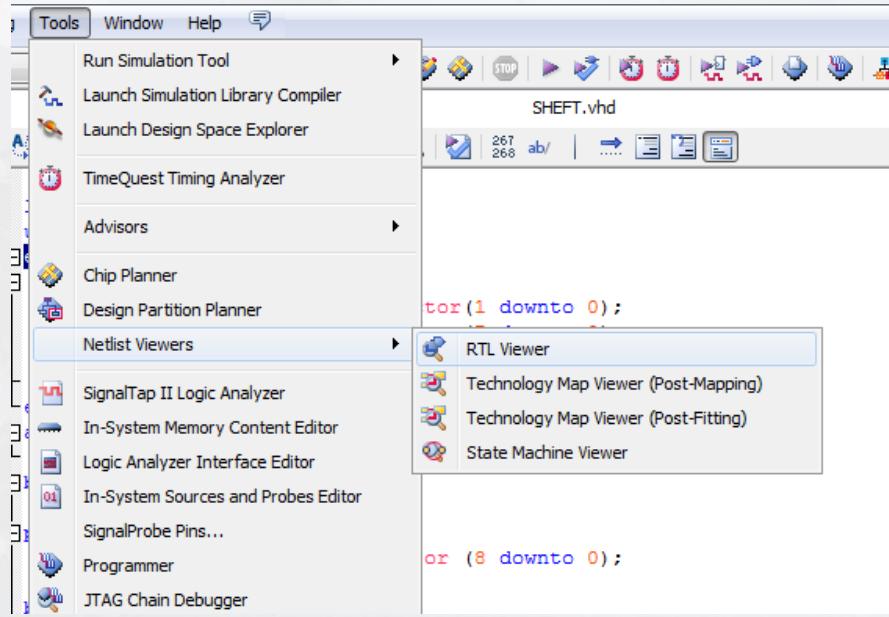

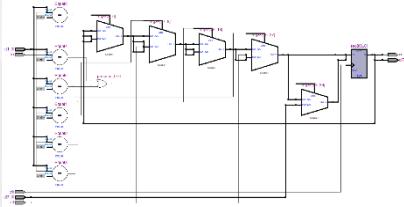

# 双向移位寄存器RTL电路图

# 实验任务与步骤

4、新建波形图文件 (\*.vwf), 设置仿真时间, 添加输入输出端口, 设置输入信号值, 保存文件。运行仿真

**建立仿真波形文件：**主菜单“File”→“New”项，选择University Program VWF，新建\*.vwf，打开波形编辑器。

**设置仿真时间：**主菜单“Edit”→“Set End Time”项。

**添加输入输出端口：**波形编辑器窗口主菜单 “Edit” → “Insert”→“Insert Node or Bus”

**运行仿真：**波形编辑器窗口主菜单“Simulation”→“Run Functional Simulation”项。

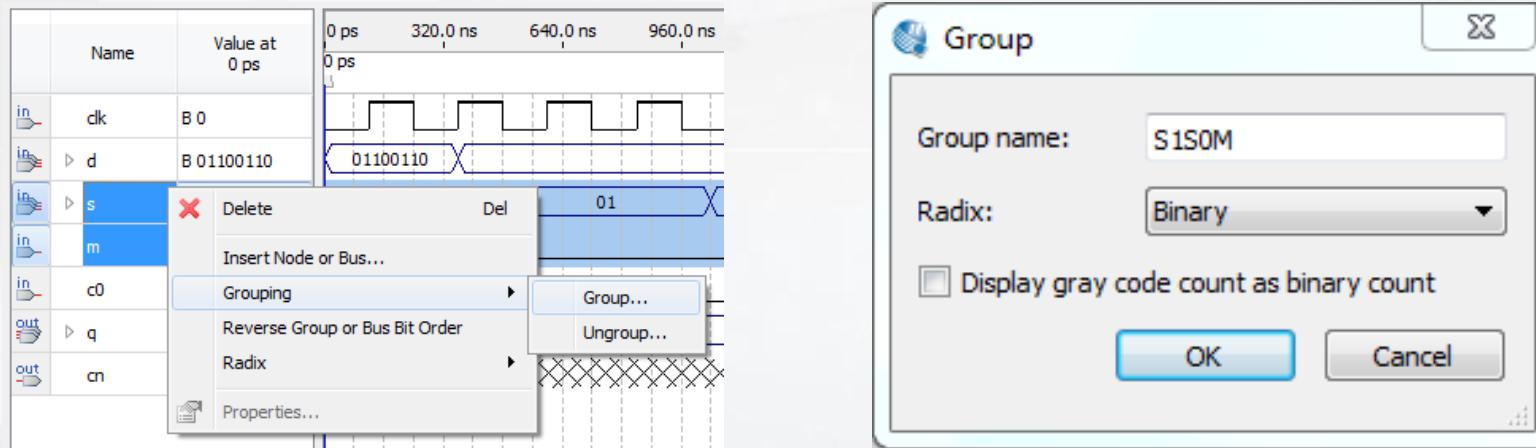

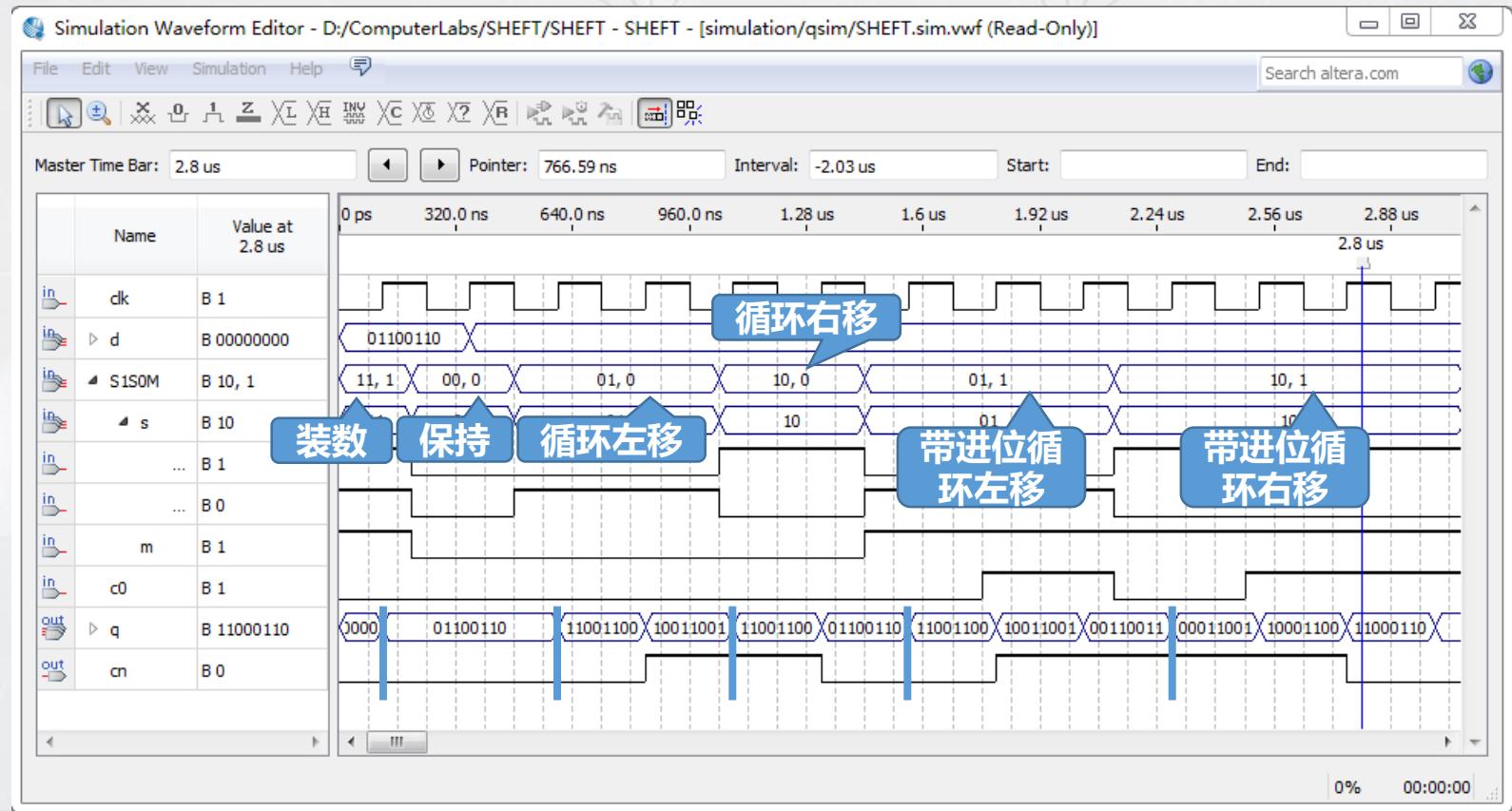

# 使用分组 (Grouping) 观察S和M信号

选中S和M，右键菜单 → “Grouping” → “Group”，组名称：S1S0M

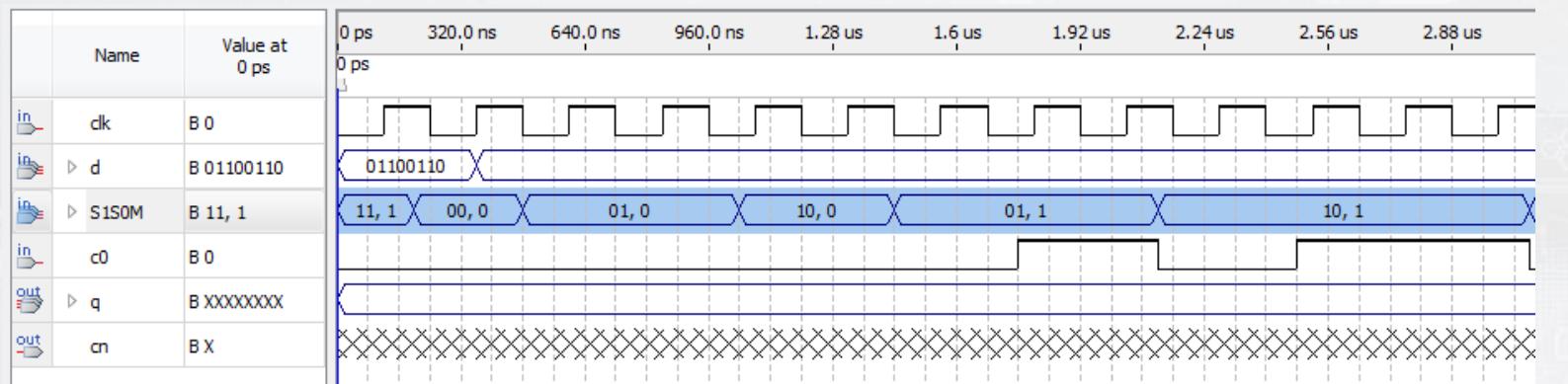

# 双向移位寄存器仿真波形图分析

带进位循环右移

# 双向移位寄存器仿真要求

- 1、装数（学号后2位，二进制8位）

- 2、带进位循环左移2次（进位为0）

- 3、带进位循环左移2次（进位为1）

- 4、循环右移4次

- 5、带进位循环右移2次（进位为0）

- 6、带进位循环右移2次（进位为1）

- 7、循环左移4次

观察q和cn

# 实验任务与步骤

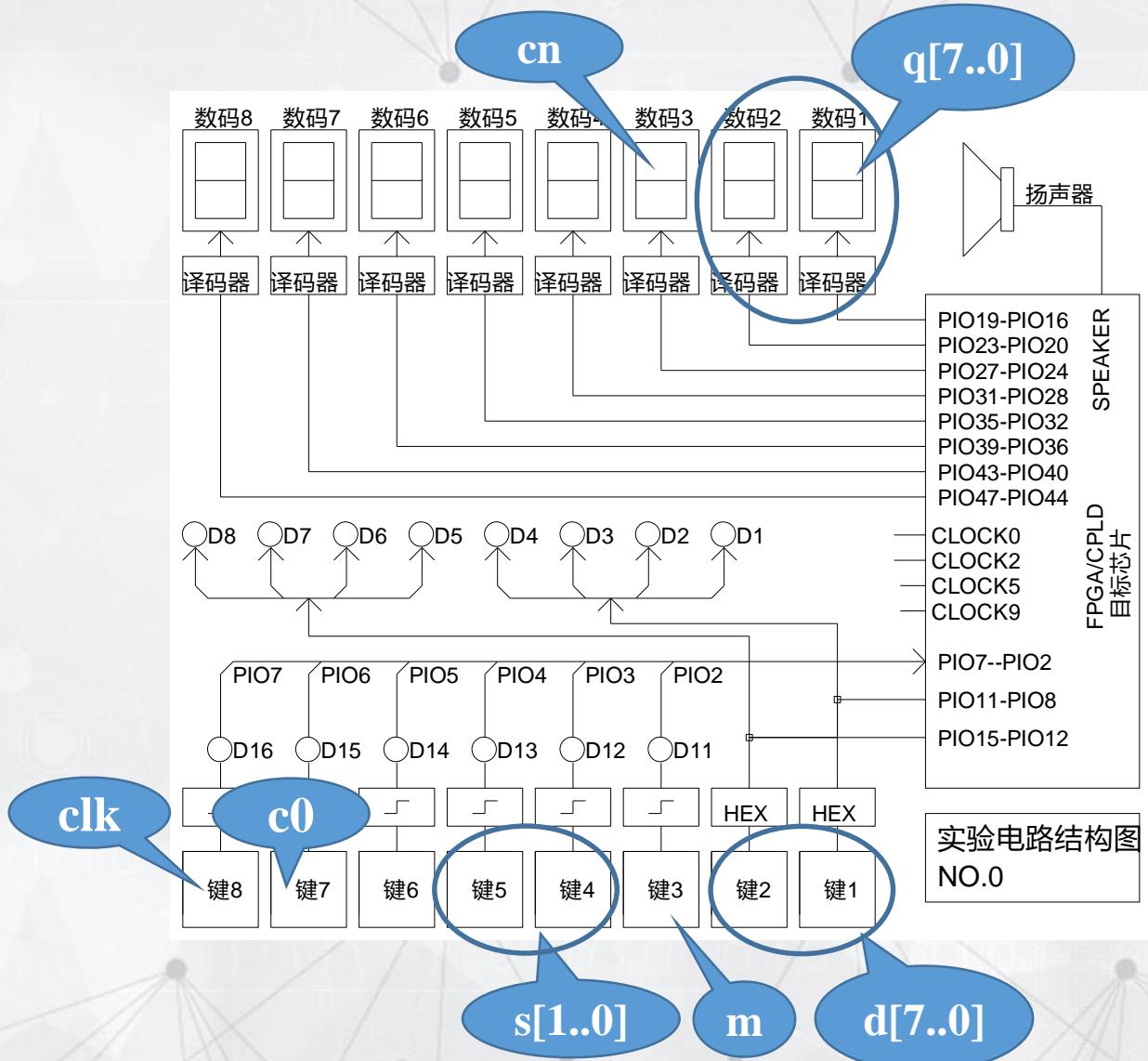

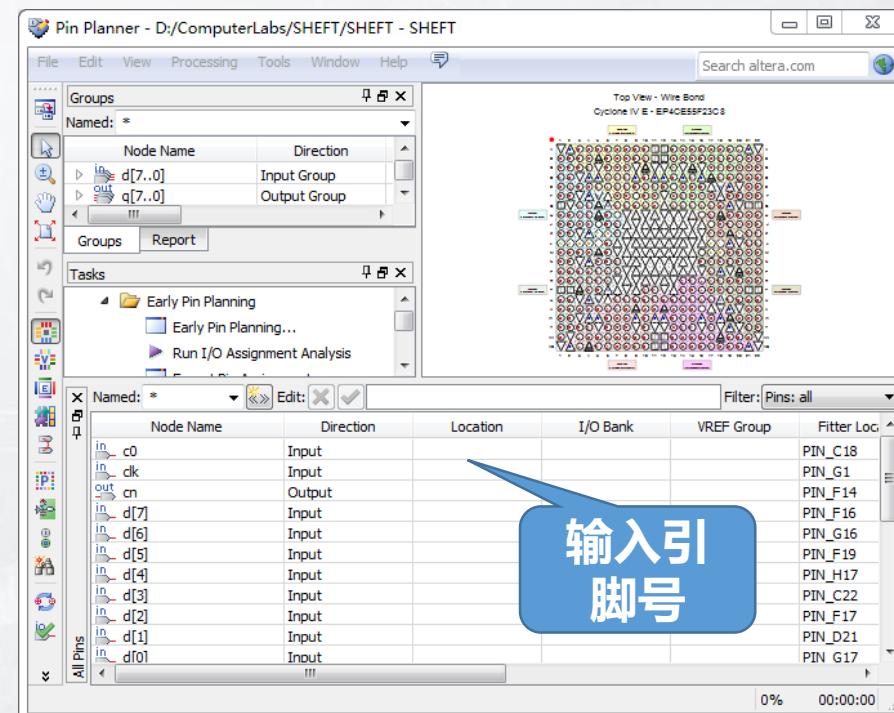

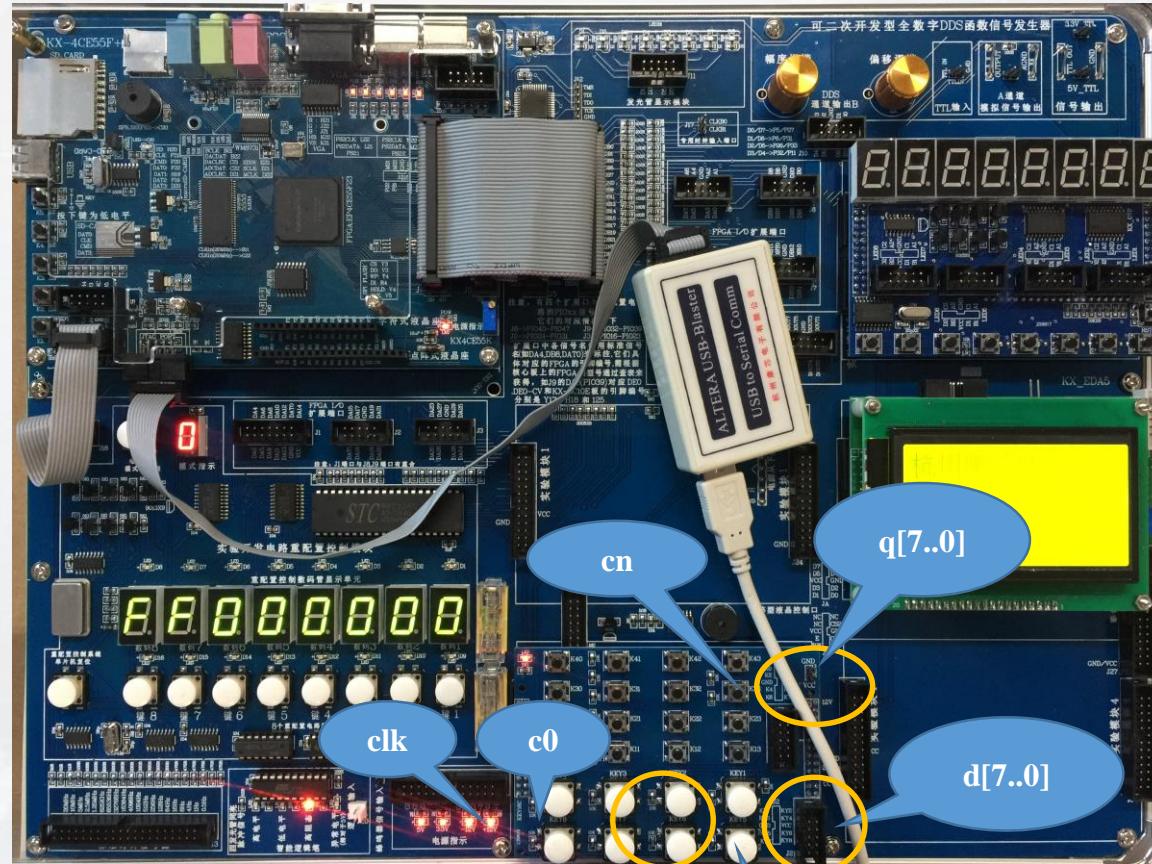

5、选择KX-CDS实验台，选择合适的电路模式结构，例如NO.0，对照电路模式图和引脚表，查找引脚号。打开编程器，输入引脚号，对电路进行引脚锁定，编译工程。

主菜单“Assignments”→“Pin Planner”项

6、下载sof文件到FPGA实验台，演示双向移位寄存器的功能。

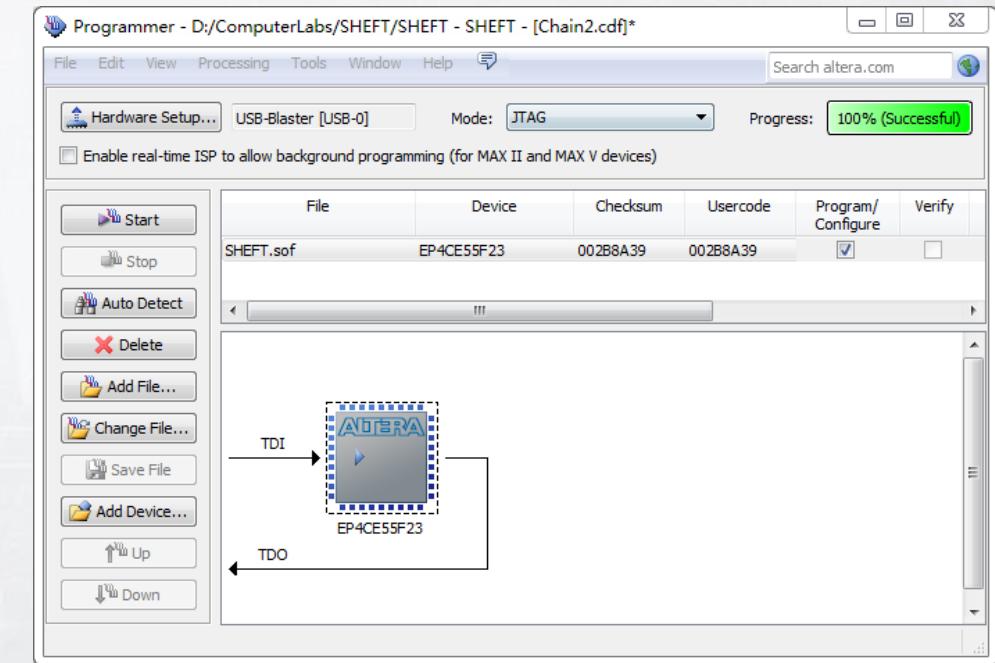

主菜单“Tools”→“Programmer”项，打开编程器，设置硬件，连接实验台。在Programmer窗口，点击Start按钮，Progress为100%时，下载完毕

# 选择FPGA实验台电路结构No.0

# FPGA实验台引脚锁定

参照电路模式图No.0，确定引脚名称，再查找引脚表，获得引脚号

双向移位寄存器引脚锁定

方案(No.0)

| 输入/输出端口 | 外设   | 引脚名称 | 引脚号 |

|---------|------|------|-----|

| clk     | 按键8  |      |     |

| c0      | 按键7  |      |     |

| s[1]    | 按键5  |      |     |

| s[0]    | 按键4  |      |     |

| m       | 按键3  |      |     |

| d[7..4] | 按键2  |      |     |

| d[3..0] | 按键1  |      |     |

| q[7..4] | 数码管2 |      |     |

| q[3..0] | 数码管1 |      |     |

| cn      | 数码管3 |      |     |

主菜单“Assignments”→“Pin”项，在

Location栏中输入引脚号

# 连接实验台下载电路

主菜单“Tools”→“Programmer”项，打开编程器，点击 “Hardware Setup” 按钮，选择USB-Blaster硬件。在Programmer窗口，点击Start按钮，Progress为100%时，下载完毕。

注意：实验台需要打开电源，并且将其JTAG接口与计算机通过USB线连接。

KX-CDS实验台

# 双向移位寄存器实验台演示

下载

KX-CDS实验台

s[1..0]

m

# 现在开始实验！（第1次课）

## 双向移位寄存器实验

- 1、参考教材102页-123页

- 2、**2个人一组。** 实体名后面加2个学号的后两位，例如sheft0709

注意，其他一些文件名，都要与实体名保持一致。否则出错。

- 3、完成后，按组验收结果。

- 4、下次课预习：基本模型机工程调试，带移位模型机原理